# Tri-band S lotted Patch Antenna design on polyimide using IC fabrication technique

Kamaljeet Singh, AV Nirmal Systems Engineering Group, ISRO Satellite Centre, Bangalore kamaljs@isac.gov.in

Abstract:

This article demonstrates the design of tri-band antenna at Ka-band on the polyimide material. Standard CMOS grade silicon wafer is lossy and results in degraded RF performance. To overcome this limitation a thick layer of polyimide is spin coated over the silicon substrate. The polyimide thickness is optimized to reduce the lossy silicon substrate effect before implementation of the same for the design of pacth antenna. The presented process is fully compatible with the standard IC fabrication and the materials selection is based on the same so as to easily integrate with the CMOS topologies. Slotted based topology of patch is presented along with the parasitic loading to have tri-band operations Fabrication methodology, theoretical aspects and simulated results are detailed in this article.

Key words: patch antenna, polyimide, tri-band, silicon substrate

#### I. INTRODUCTION

Patch antenna are extensively used in satellite communication, radar, navigation receiver, bio-medical radiator, missile telemetry, radio altimeter, weapon fuzing etc. Modern communication system demand compact size, conformity, simpler topology and efficient microwave circuits which can be used for multiband applications as well as in modern wireless communication systems.[1-2] This demand leads to develop antenna with low profile, small size, ease of processing and integration with other sub-system. Multiband antenna can be realized using various topologies such as fractal geometry, defected ground plane, groove, tuning material, shorting pins, slots using single layer or multilayer approach. Compared to other approaches such as shorting pins, spurline filter with perturbation technique leads to complexity whereas slotted antenna using single layer is easier implementable and integratable. Low possibility of surface wave excitation, low sensitivity towards manufacturing tolerances, less spurious excitation and radiation fields in both uni- and bi-directional are some of the advantages of slot antenna. In future communication systems the necessity is to have compact trans-receiver circuits integrated with the active topologies and silicon is the preferred alternative. Standard CMOS integrated circuit processing is desired consisting of RF/digital/analog functions on the same chip for low cost and high volume production at these frequencies. However, traditionally microwave circuits realized on the low resistivity silicon substrate exhibits high loss i.e CMOS grade Si wafers. This problem can be alleviated by using high resistivity silicon as found out by Buechler et al[3]. But HRS(high resistivity silicon) are not only costlier but they have more dielectric loss associated with them. As at high frequency, the dielectric behaviour of the silicon substrate assuming to be resistive is no longer valid below the dielectric relaxation frequency defined as

where Rsub and Csub are the resistance and capacitance of the substrate and  $\rho_{Si}$  and  $\varepsilon_{Si}$  are the resistivity of the substrate permittivity and of the substrate, respectively.[4]This relation shows strong dependency of the doping on the fc. To circumvent this phenomena various mitigation techniques such as high resistivity silicon, thick layers of oxide and nitride, bulk micromachining, epi layer, trench is proposed. These prevalent techniques are either incompatible to the IC fabrication process, higher cost implications or leads to higher intrinsic stresses. Alternatively, polyimide is proposed in this article to overcome the losses associated with the silicon substrate and fully compatible with the IC fabrication process. Further the permittivity of the polyimide results in overcoming the limitations imposed by the high permittivity silicon substrate in antenna realization.

In this article tri-slot antenna is proposed to achieve patch operations at three different frequencies on polyimide. The slots reported are H-,C-,U-shape to achieve the desired specifications but in the present article two vertical slots along the length and a diagonal slot based topology on polyimide is designed to achieve tri-band operations at Kaband. These slots can be easily adjusted to improve the parameters such as return loss, VSWR and radiation pattern. Detailed design aspects, fabrication methodology, theoretical and simulation is presented in this article.

### II. EFFECT OF DIELECTRIC LAYERS

The patch design is based on the combination of the silicon substrate (0.675 mm) beneath various layers which are compatible with the IC processing techniques. Antenna substrate parameters for antenna applications are: dielectric constant, loss tangent, useful temperature range, thermal conductivity, coefficient of thermal expansion, water absorption, volume resistivity, dielectric strength, flexural strength, tensile strength, mach inability and solder ability. The attenuation constant can be found out to be

$$\alpha = \omega \sqrt{\frac{\mu \varepsilon}{2}} \left( \sqrt{1 + \frac{\varepsilon''}{\varepsilon'}} - 1 \right) \text{ where } \varepsilon' = \varepsilon_r \varepsilon_0 \text{ and } \varepsilon'' = \frac{\sigma}{\omega \varepsilon}$$

.....(2)

This relation shows considerably electric field at the bottom surface compared to the top which can excite substrate modes and can effect the bandwidth of operation [5]. It can be overcome by employing thick dielectric layer over the lossy silicon substrate. A comparative analysis regarding insertion and return loss is carried out for the microstrip line over polyimide, nitride and oxide layer as shown in Table1. It can be seen that a thick layer around 5 um can effectively reduce the substrate effect and the performance is at par with the alumina substrate.

TABLE I Analysis of layer effect on RF performance

| Feature                      | HR-<br>Si<br>(675<br>um) | Alumina<br>(650<br>um) | Oxide<br>(5um)<br>over<br>Si(675<br>um) | Polyimide<br>(5um)<br>over<br>Si(675 um) | Nitride(5um)<br>over Si(675<br>um) |

|------------------------------|--------------------------|------------------------|-----------------------------------------|------------------------------------------|------------------------------------|

| Insertion<br>Loss<br>(dB/mm) | 1.3                      | 1                      | 1.01                                    | 1.01                                     | 1.01                               |

| Return<br>Loss (dB)          | <25                      | <25                    | <25                                     | <25                                      | <25                                |

Thick layers of oxide and nitride are deposited with the PECVD process and needs multiple processing steps. Also high resistivity silicon substrate is expensive (30 times) compared to standard silicon substrate[6]. Alumina is not suitable for antenna applications due to associated high resistivity. The other considerations are the permittivity and process compatibility for which nitride and oxide are not suitable. Polyimide is an attractive option due to low permittivity, compatible fully with CMOS process, ease of deposition due to spin coating process [7]. The various modes of propagation in microstrip line are

Skin effect mode (zero resistivity) Dielectric quasi-TEM mode (high resistivity) Slow wave mode (moderate resistivity)

**<u>Dielectric Quasi-TEM mode</u>**: product of freq. and resistivity of the semiconductor subs. is large enough to produce a small dielectric loss tangent, the substrate acts like a dielectric and  $E_t$  and  $H_t$  penetrate freely into the semiconductor substrate.

<u>Skin-effect mode</u> : product of frequency and substrate conductivity is large enough to yield the small penetration depth into the substrate, the substrate behaves like a lossy conductor wall. Neither  $H_t$  nor  $E_t$  can penetrate the semiconductor substrate.

<u>Slow-wave mode</u>:  $H_t$  freely penetrates into the semiconductor substrate while  $E_t$  doesn't. It is when frequency is small compared to dielectric relaxation frequency and depth R of quasi-static field penetration is small compared with the skin-depth of the substrate.

The thickness of the polyimide needs to be optimized so as to result in the dielectric quasi TEM mode of propagation making the permittivity of the polyimide prominent compared to the silicon.

# III. DESIGN METHODOLOGY

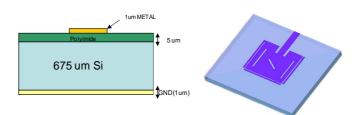

The two critical steps in designing the patch antenna were the definition of the patch dimensions and the feeding configuration Feeding mechanism plays an important role in the design of microstrip patch antennas. Instead of feeding using microstrip line, aperture coupled, proximity coupling in this article inset feed microstrip line is employed. The patch dimensions have direct influence on the operating frequency and on the antenna gain. Physical parameters of the antenna (Fig 1) like patch width (W), length (L) and input port impedance are evaluated using standard design equations from the transmission line model (TLM) approximation as given in eq (3).[8]The patch dimensions are calculated taking into considerations of the effective permittivity of polyimide and silicon substrate. The antenna performance such as gain, bandwidth and efficiency can be enhanced by employing thick substrate with lower dielectric constant due to loosely bound fields for radiation. Instead of employing silicon substrate which results in poor efficiency and the bandwidth due to surface wave excitation, a thick layer of polyimide can overcome this limitation by reducing the effective permittivity.

Fig1: Patch antenna geometry on polyimide layer

$$W = \frac{v_0}{2f_r} \sqrt{\frac{2}{\varepsilon_e + 1}}$$

$$L = \frac{v_0}{2f_r \sqrt{\varepsilon_e}} - 2\Delta L$$

$$\Delta L = 0.412h \frac{(\varepsilon_e + 0.3) + (W/h + 0.264)}{(\varepsilon_e - 0.258) + (W/h + 0.8)}$$

$$Z_0 = R_{in} \cos^2\left(\frac{\pi}{L} \times y_0\right)$$

(3)

where  $\varepsilon_e$  is the effective permittivity,  $y_0$  is inset feed notch distance,  $v_0$  is speed of light ,h is height of the substrate and  $R_{in}$  is input resistance at  $y_0$  which is the position of the feed from the edge along the direction of the length (L) of the patch. The circuit is optimized using e-m simulator as accurate prediction of the patch dimensions is difficult due to fringing fields effect together with the small size of the ground plane. Appropriate slots dimensions along with the parasitic loading are incorporated to achieve the performances at the Ka-band. Slots in the microstrip line increases the inductance which enhances the bandwidth also.

# IV. FABRICATION ASPECTS

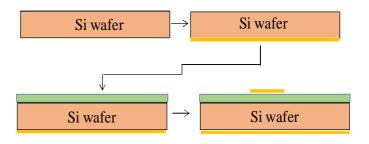

The circuit is fabricated on the standard silicon wafer followed by the polyimide deposition. Metal is deposited using the sputtering process followed by patterning. Polyimide is spin coated and baked before repeating the coating to achieve the desired thickness [7]. Proposed fabrication steps are detailed below:

- a) Starting material (High-Resistive Si of 675 µm thickness)

- b) Polyimide deposition using spin coating (5 um)

d) Aluminium sputtering (top and bottom) and patterning on top side only (2 $\mu m)$

e) Dicing, assembly and packaging

The limitation in the CMOS processing is the limited thickness of the metal layer as well as non usage of gold layer. Sputtering and evaporation are the standard technique for metal deposition but these are tuned for the thickness of around 1 um. In RF application the skin depth phenomena plays an important role in ohmic loss consideration. As the polyimide is employed as a negative photoresist in the CMOS process so the process is totally compatible without incorporating any extra fabrication steps.

Fig2: Various fabrication steps for patch antenna realization on polyimide

### V. DISCUSSIONS

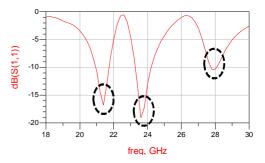

The circuit is simulated using the standard tool based on MOM methodology. The dimensions and loading is optimized to achieve the performance at tri-band frequencies as shown in Figure 3.

Fig 3: Simulated response of switch in up and down state

The performance shows the peaks at 21.5GHz, 23.5 GHz and 28 GHz where at higher end the performance is degraded due to surface wave excitation. The performance can be improved by employing a stack of standard oxide and nitride beneath the polyimide layer which can reduce the effect of field penetration in the lossy silicon substrate. Further the efficiency of the antenna can be enhanced by employing the bulk micromachining technique for which the polyimide layer can be used as etch stop layer.

VI. CONCLUSION

This article presents design of a tri-band patch antenna at Ka-band on polyimide layer supported by silicon substrate. The present architecture uses the concept of slot along with the parasitic loading to achieve the desired performances. The novelty of the present concept lies in the implementation methodology which is totally CMOS compatible. Also theoretical analysis of the proposed structure is explained to implement the same methodology for higher frequencies. Bulk micromachining concept can be implemented in the same topology and can be filled with another material which can scale the frequency. Also tunability can be achieved by implementing the switches at the radiating edges.

#### ACKNOWLEDGEMENT

Authors gratefully acknowledge Director, ISAC for his support and encouragement. Also thanks to colleagues at ISRO for technical discussions.

#### REFERENCES

- 1. C A Balanis," Antenna Theory: Analysis and Design," Harper & Row publisher,1982

- 2. G M Rebeiz, *RF MEMS Theory, Design and Technology*, John Wiley & Sons, 2003

- 3. *Principle of RF and its applications in MEMS switches*, Kamaljeet Singh, under publication

- Joseph Buechler, Kasper et al," Silicon High-resistivity substrate millimeter wave technology," IEEE Trans. MTT, Vol34, No.12, pp1516-1521, 1986

- John Papapolymerou and G E Ponchak," Microwave Filters on a low resistivity Si substrate with a polyimide Interface Layer for Wireless Circuits," IEEE Radio Frequency Integrated Circuits Symposium-2001, pp 125-128

- Kamel Benaissa, J Y Yang et al," RF CMOS on High-resistivity substrates for System-on-chip Applications," IEEE Trans. On Electron Devices, Vol.50., N03, pp 567-576, 2003

- Kamaljeet Singh, D Bhatnagar and S.Pal," CAD oriented study of Polyimide interface layer on Silicon substrate for RF applications," RF Cafe, May 2007,pp 30-35

- 8. CAD of Microstrip Antennas for Wireless Applications, Robert A. Sainati, Artech House

*Kamaljeet Singh* has obtained M. Tech (Microwaves) from Delhi University in 1999 and awarded PhD in 2010. He joined ISRO Satellite center, Bangalore in 1999 where he worked in GEO-receiver. From August 2006 –

Feb 2016 he was posted in Semi- Conductor Laboratory, Chandigarh and worked in the areas of RF-MEMS and sensors. He is presently working in SEG group at ISAC and delivering RF packages for TTC transponders.

A V Nirmal obtained his B.E in Mechanical Engineering from Kerala University in 1984. He joined VSSC, Trivandrum in1984 and has been working in ISAC since 2004. He is credited with productionzation and delivering of all sub-systems of IRS and Geosat missions. He was involved in the design and development of various mechanical systems for both

Launch vehicle and satellites and establishment of test facilities. He is presently working as Group Director, Systems Engineering Group, ISRO Satellite Centre